Biography

Chuxu Guo is an FPGA application engineer intern at AMD University Program and a master student of electronic engineering at ShanghaiTech University (advised by Prof. Yajun Ha). His research interests include FPGA hardware accelerator and software-hardware co-design. He is currently working on the project of defect detection in the field of semiconductor manufacturing. He is also interested in the field of pointcloud accelerator, lightweight encryption IP and reconfigurable computing. Email: guochx2022@shanghaitech.edu.cn & chunxug@amd.com.

Interests

- Defect Detection

- Pointcloud Accelerator

- Lightweight Encryption IP

- Reconfigurable Computing

Education

MEng in Electronic Engineering, 2025

ShanghaiTech University

BEng in Electronic Engineering, 2022

ShanghaiTech University

Experience

FPGA Application Engineer Intern

Responsibilities include:

- Developing open-source FPGA remote access framework

- Developing PYNQ-based FPGA accelerator reference design

- Delivering FPGA training to students

FPGA Application Engineer Intern

Responsibilities include:

- Supporting academic users in PYNQ-based FPGA accelerator development

- Developing customized composable pipeline with DFX for video processing

Accomplishments

AMD Asia Technical Conference (AATC) 2023 Honorable Paper

In this paper, we proposed a solution by using Zynq device with PYNQ open-source framework, JupyterLab, and NFS board management to build a remote FPGA application design system in a light way. The system supports the RTL ,HLS design flow, provides an interactive GUI for new users to learn and practice.

Projects

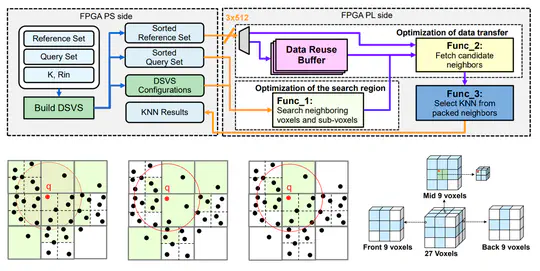

Existing KNN accelerators perform inefficiently in reducing search regions and transferring point cloud maps. To solve this issue, we propose a fast and energy-efficient KNN accelerator with two techniques. First, we propose a novel search technique (NSVS, nearest-sub-voxel-selection) to reduce the redundant search region. Second, we design an adaptive data transfer technique to efficiently transfer point cloud maps with different data reuse ratio from external memory to accelerator via multi large-bit-width ports. Experimental results show that our proposed KNN search accelerator achieves 9.1 times faster than state-of-the-art KNN implementations on FPGA. This work is published in ICECS 2023.

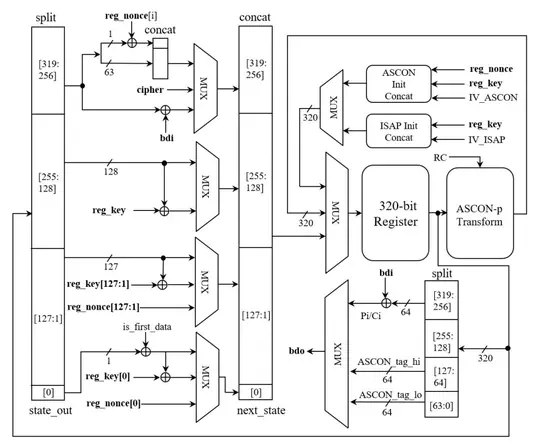

Electronic control units (ECU) have been widely used in modern resource-constrained automotive systems, communicating through the controller area network (CAN) bus. However, they are still facing man-in-the-middle attacks in CAN bus due to the absence of a more effective authentication/encryption mechanism. To defend against the attacks more effectively, we propose a unified lightweight authenticated encryption that integrates recent prevalent cryptography standardization ISAP and ASCON.Experimental results show that our proposed unified lightweight authenticated encryption can reduce 26.09% area consumption on Xilinx Artix-7 FPGA board compared with the state-of-the-arts. This work is published in ICECS 2022.